文章图片

点击蓝字 关注我们吧~

ntel日前公布其未来制程技术发展布局 , 除了现有纳米(nm)等级制程设计 , 接下来也会开始布局埃米(?)等级制程技术 , 预计最快会在2024年进入20A制程技术 , 另外也计画在封装技术持续精进 , 让处理器设计尺寸能持续微缩 。 而在EDM 2021国际电子元件会议中 , Intel更进一步说明其封装技术将以超过10倍密度提升为目标 , 其中将使晶体管密度提升30% , 并且让处理器设计尺寸能减少50% , 进而在2025年持续推动摩尔定律发展优势 。

依照Intel说明 , 未来疆界由混合键合(hybrid bonding)技术 , 让封装内互连密度提升10倍以上 , 而晶体管密度能提升30% , 并且让处理器设计尺寸缩减50% , 更计划透过颠覆物理概念让处理器供电、内存技术有明显突破 。

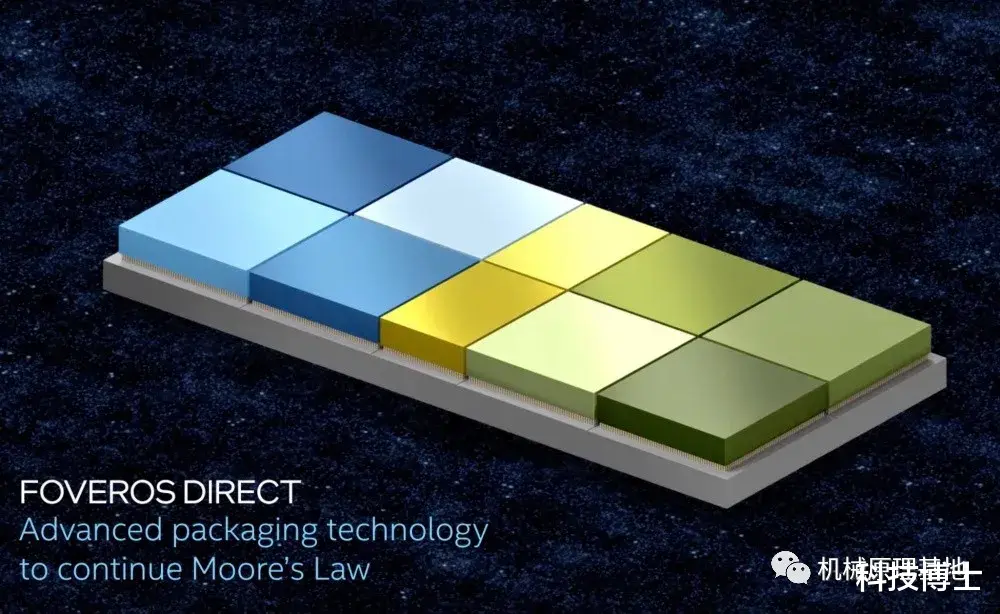

同时 , Intel也再度强调摩尔定律依然存在 , 并且随着运算创新持续提升 , 更强调目前已经透过应变硅、Hi-K金属闸极、FinFET、RibbonFET , 以及包含EMIB、Foveros Direct等封装技术创新 , 让处理器能依照摩尔定律持续演进 。

延续今年7月宣布未来制程技术发展布局 , Intel表示将以Foveros Direct封装技术 , 借此实现10微米以下的凸点间距 , 让3D封装技术能对应更高互连密度 , 同时也将与业者合作推动新设计与测试标准 , 让混合键合设计微型芯片能成为广大生态 。

另外 , 透过以环绕式闸极(gate-all-around)的RibbonFET设计 , 将透过多组晶体管堆叠方式 , 在每平方毫米放入更多晶体管 , 目标达成最高30%至50%的逻辑微缩提升 , 接下来更计划在2024年进入埃米设计阶段 , 透过仅有数个原子宽幅的新材料设计 , 实现打造克服传统硅通道物理极限的电晶体 , 藉此让未来10年运算发展能大幅增长 。 而在300mm面积晶圆上 , Intel更以氮化镓 (GaN)供电设计为基础 , 藉此推进更有效率的供电技术 , 让电晶体能透过低损、高速传递的供电向绿运作 , 同时也能降低主板等供电元件占用空间 。至于透过新型铁电材质 , 亦可实现读写延迟更低的嵌入式动态内存设计 , 藉此配合新处理器设计提升运算效率 。 在此次EDM 2021国际电子元件会议中 , Intel更计划以全新物理设计取代传统金属氧化物半导体场效晶体管(MOSFET)设计 , 其中包含以在一般室温下运作 , 并且以实验性设计的磁电自旋轨道(magnetoelectric spin-orbit、MESO)逻辑装置实作 , 借此诠释基于开关纳米规模磁铁设计的新型晶体管可制造性潜力 。 针对接下来的量子运算设计 , Intel更展示与CMOS生产制造兼容 , 藉此实现可扩展量子运算的完整300mm量子制程流程 , 并且确定未来研究的下一步 。

【CPU|Intel以新制程、供电与材质设计提高处理器晶体管密度,持续推动摩尔定律发展】

如果您觉得我们的文章有传播价值 , 请点击右上角的“发送给朋友”或“分享到朋友圈”来分享给更多的朋友!也欢迎您邀请更多的朋友们加入我们!

相关经验推荐

- 小米科技|Intel/AMD/NV等撑不住!CPU、GPU等今年都要大涨价

- 小米科技|2022拍照最好的几款手机,堪比小单反,经常拍照的可以考虑一下

- 三星|三星 Note 20 系列可以升级 One UI 4.0 正式版了!流畅度大增

- 飞利浦·斯塔克|苹果iPhone SE3机模放出,果粉眼睛一亮:这才是梦寐以求的手机

- 华为鸿蒙系统|鸿蒙功耗很不错,比以前耐用一些,系统也增加了一些小功能

- 小米科技|小米手机用一年了,现在电池严重不行,10%以下就自动关机

- 摩托罗拉|1亿像素+30倍变焦+骁龙778G,跌至1548元,千元机拍照也可以很强

- 2g|笔记本耗电量低,所以CPU采用低电压版本,速度上就比台式机慢

- 5G|人工智能和5G被列为2022年及以后最重要的技术趋势

- 阿里巴巴|Intel计划以代号Bonanza Mine的ASIC架构处理器跨入挖矿热潮