文章图片

【半导体|华林科纳半导体-优化缩短3D集成硅通孔(TSV)填充时间的创新方法】本文介绍了一种新型的高纵横比TSV电镀添加剂系统 , 利用深层反应离子蚀刻(DRIE)技术对晶片形成图案 , 并利用物理气相沉积(PVD)技术沉积种子层 。 通过阳极位置优化、多步骤TSV填充过程、添加剂浓度和电镀电流密度优化 , 在保持无空隙填充轮廓的同时提高填充效率 , 通过tsv的晶片段电镀验证了其可用性 。 利用线性扫描伏安法(LSV)、计时安培法和数值模拟方法研究了其作用机理 。

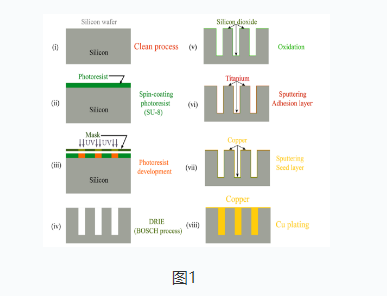

对于本文开发的原型器件 , 设计了四种图案晶片 , 其中包括050μmx 150μm040μmx 140μm 030umx 130μm和020μmx 120um.的视孔如图1所示 , TSVs通过六种工艺创建: (a)硅片清洗; (b)旋转涂层光刻胶(SU-8) ; (C)光刻抗蚀剂开发; (d)深反应离子蚀刻(DRIE) (博世工艺) ; (e)氧化获得二氧化硅阻挡层(提供TSVs之 间的电隔离) ; (f)溅射钛粘附层; (e)溅射铜种子层; (h)Cu-TSVs电镀 。 图2显示了使用玻色工艺蚀刻的透硅孔的扫描电镜显微图 , 图2(a)和(b)分别显示了tsv的顶视图和横截面SEM显微图 , 如图2(C) ,所示扇贝的横向粗糙度小于100纳米 。

利用商用的COMSOL多物理软件模拟了TSV中的电场分布 , 采用有限元法(FEM)建立了物理模型在该模型中 , 与TSV的段晶片阴极对应的阳极位置是可变的(阴极的上、下或右侧) 。

本文介绍了-种新型的用于填充高宽径比TSV的商业添加剂体系碱电解质含有80gL-1Cu2+、20gL-1CH3SO3H和50mgL-1Cl-提出了四种不同的创新方法来缩短填充时间 。

电化学测量采用了-种标准的三电极系统 , 使用图案和固体平面电极作为工作电极(WE) Pt网用作对电极(CE) , 采用饱和热量参比电极(SCE)作为参比电极 , 本文给出的电位相对于SCE (0.242V相对于正常的氢电极(NHE) ) , 电镀电池中电解质的体积为250mL , 由于扩散能力、添加剂消耗与电流密度之间的关系 , 电流密度影响填充模型和填充效率 。 在含有4ppmDVF-B、20ppmDVF-C和1.5ppmDVF-D的电解质中 , 不同电流密度下cu-tsv电镀的截面光学显微镜图像 。当同时加入三种添加剂(DVF-B、DVF-C、 DVF-C、 DVF-D)时 ,电流密度对通过填充行为影响显著 , 当在电镀过程中施加较低的电流密度(3mAcm- 2)时 , 该抑制剂具有较弱的抑制作用 , 沉积速率缓慢 , 且抑制因子在通过底部区域的消耗量较小 , 更重要的是 , 有足够的时间让抑制剂扩散到通道的底部 , 添加剂的添加量(DVF-B、DVF-C和DVF-D)在通过深度方向上几乎相等 , 因此在低电流密度下 , 填充行为表现出保形填充特征 。

在较高的电流密度(10-20mAcm- 2)时 , 沉积速率增加 , 抑制剂每秒的消耗量增加 。 虽然抑制因子的扩散系数是恒定的 , 但抑制因子没有足够的时间来扩散到通道的底部来补充消耗抑制因子 , 虽然加速器的数量在通道内部的任何地方都是相等的(由于加速器的扩散系数很大) ,但抑制剂的剂量由于抑制因子的消耗和扩散的限制 , 沿着通过深度方向显著减少 , 这种沿通过深度方向的添加剂分布导致了电镀的超填充类型 。

从填充曲线上可以看出 , 在相同数量的电荷(Q=Ixt)下 , 铜沉积量(S)随着应用电流密度的增加而减少 , 这可能是由于电流效率(η) 的降低所致 , 这可能是由于抑制因子的抑制作用随着外加电流密度的增加而增加所致 。

用固体平面电极和图案化电极测量的LSV曲线 , 分别大致对应于通道的顶部和通道的底部 , 通道底部区域的电流密度大于顶部区域的电流密度 , 通道底部和通道顶部的镀速率差小而小 , 在适当的电流密度(ca)下 , 通道底部和通道项部之间的电镀速率的差异显著增加 , 可以抑制通道中空的形成 , 以上讨论表明 , 适当的电流密度不仅避免了通过口中形成的接缝或夹口 , 而且提高了通填效率 。

相关经验推荐

- 华为鸿蒙系统|蒙系统的那些卡片功能,也就是刚面世时候的噱头,用下来用处不大

- AirPods|感谢华强北,给了AirPods第二次生命

- 华为|不可否认,华为做的事情,客观上让我们有了一个好的标杆

- 华为荣耀|9999元起售!国产“折叠屏性能王”诞生,荣耀逐步收复华为失地

- 华为鸿蒙系统|鸿蒙功耗很不错,比以前耐用一些,系统也增加了一些小功能

- 红米手机|中国的操作系统路在何方,华为鸿蒙系统普及路难, 新plug操作系统

- |1999元把\我妻善逸\带回家 华硕X鬼灭之刃限定版电竞路由新品上市

- 华为|华为上架新机,搭载麒麟芯片,5000mAh仅售1399元

- |创小报151: 华为进军私募;蚂蚁减持众安保险;佳能进军造车;马斯克

- 华为|2021年,最大苹果的三大槽点