文章图片

文章图片

集微网消息(文/思坦) , 巧或不巧地 , 3月初 , 因Apple Silicon分道扬镳的英特尔和苹果 , “联手”将风光已久的先进封装 , 再次推上风口浪尖——

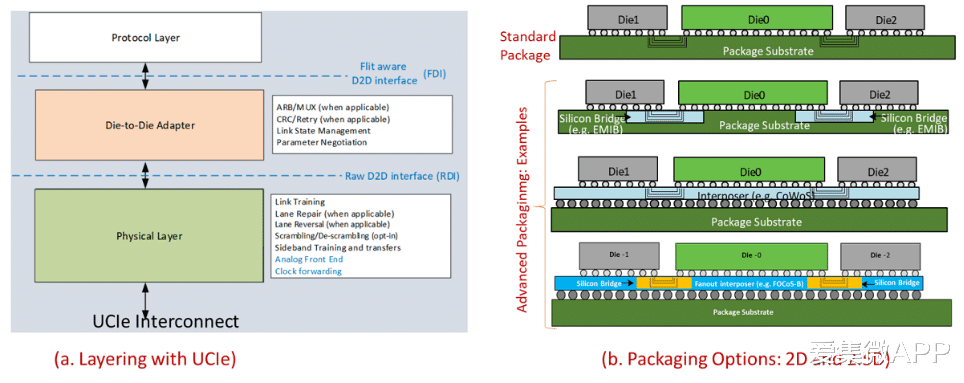

先有英特尔联合十大行业巨头官宣通用Chiplet高速互联标准UCIe , 后有苹果发布史上最强M1 Ultra芯片 , 最大卖点落于封装架构UltraFusion 。

从本质上来说 , UCIe是生态层面的统一接口IP标准 , UltraFusion是物理层面的键合技术 , 但从目标来看 , 两者均瞄准于Chiplet“乐高化”的最大痛点——D2D(die to die)互联 。

苹果向左:键合技术硬核推进

如果说Chiplet是大楼 , 那么接口IP就类似于楼梯间 , 键合技术则是楼梯 , 两者结合负责每一楼层(即die)的互联 。 在技术路线尚未统一的当下 , 各方在实现die to die互联技术的尝试各有不同 。 UCIe联盟中 , 苹果和英伟达的缺席 , 或许正代表来了这种分歧 。

作为台积电InFO先进封装解决方案最著名一战的客户方 , 苹果将其先进封装技术的锚点选在键合技术上 , 并不难理解 。 根据集微网从厦门云天获得的一份调研报告显示 , 这个细节被苹果以“采用硅中介层进行互联”一笔带过的UltraFusion封装技术 , 其中实现的突破 , 足以带来互联技术的内部地震 。

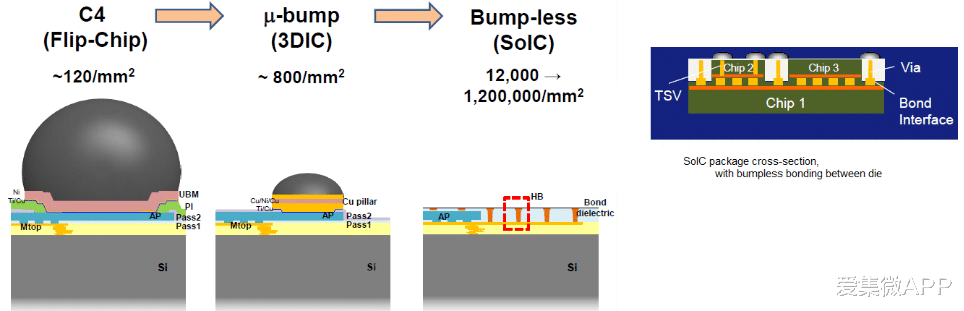

与此前业内猜测的无凸点键合技术不同 , UltraFusion仍然建立在微凸点的设计上 , 但主要做出了下图所示的六大改进 , 而其中帮助苹果成为业内首个实现GPU裸片互联的最关键在于中介层实现的高密度互联以及Die-Stitching(裸片缝合)技术 。

图源:厦门云天

GPU裸片互联难点在于消耗的内部带宽过高 , UltraFusion基于台积电第五代CoWoS-S技术 , 两个裸片通过中介层布线传输超过10000个信号 , 连接密度是现有技术的两倍 , 提供的2.5TB/s超高处理器间带宽(是其他互联技术带宽的4倍多)有效解决了带宽问题 。

更大的光罩尺寸也为两颗GPU裸片腾出了空间 , 据了解 , 台积电第5代CoWoS-S技术达到了大至三个全光罩尺寸(~2500mm2)的水平 , 作为对比 , 英伟达4年前集成了HBM的GPU , 光罩尺寸仅为815mm2 , 台积电为此采用了裸片缝合技术 。

目前尚不清楚在UltraFusion上来自苹果的研发占比 , 鉴于英伟达、AMD预计也将于今年依托于台积电技术推最新一代GPU , 抢先实现GPU裸片互联的苹果必然有所依仗 。 虽然苹果于去年才获得其第一个先进封装专利 , 但其与台积电早已携手在这一领域进行研发 , 对终极技术的追求也比想象的更远 。

无凸点键合是苹果目前仍在追求的技术突破方向 。 厦门云天董事长于大全教授对笔者表示 , 苹果很早就开始与台积电共同研究无凸点键合方法 , 主要特征是不再使用后道集成所用的凸点 , 转而直接将裸片类似于“铜对铜”地堆叠到一起 。 这种方法除了没有“凸点间距”这一紧箍咒外 , 还能大大降低热阻 。

从C4凸点到无凸点;图源:台积电

【苹果|【芯观点】2.5D/3D封装互联:苹果向左走,英特尔向右走】另外耐人寻味的是 , 今年以来 , 苹果官网已发布多条与先进封装相关的职位 , 其中一个名为“先进封装开发工程师”的职位 , 要求应聘者有至少10年的晶圆厂集成工作经验 , 其中至少5年的先进封装工作经验 , 具有BEoL工艺、RDL、细间距微凸点、混合键合、TSV等裸片互连工艺集成经验 。

相关经验推荐

- 苹果|什么蓝牙耳机好?好评蓝牙耳机排行

- 大屏|代号马里亚纳海沟!中企自研芯片令硅谷慌乱,抱怨白宫搞砸一切

- 罗永浩|换条道路收购苹果?罗永浩即将回归科技行业,但公司不再叫锤子

- 芯片|VR绘画应用《Vermillion》将于3月24日上线Quest平台

- 荣耀|三度停滞,苹果造车到底在纠结什么?

- |友商彻底爆发,骁龙870手机降至1489元,还有144Hz高刷和50倍变焦

- 苹果|欧盟法案或要求苹果开放侧载,iOS生态要变天了?

- 苹果|苹果13mini支持双卡吗?这点遗憾不能忍

- |剪辑修图都能用,HKCT2751U显示器点评!

- 苹果|苹果自研的ios系统,拥有强大的应用平台,应用几乎可以做任何事情