【芯片|中国显卡厂商芯动科技加入UCIe联盟:首发国产Chiplet标准方案】

文章图片

文章图片

自称中国一站式IP和定制芯片领军企业的芯动科技宣布 , 正式加入UCIe产业联盟 , 推动Chiplet(小芯片/芯粒)标准化 。

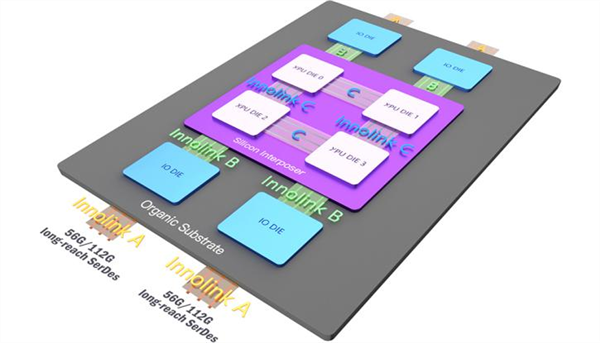

同时 , 芯动科技自研的首套跨工艺、跨封装物理层兼容UCIe国际标准的Innolink Chiplet解决方案 , 已在全球范围内率先兼容各种应用场景 , 并成功商用落地 。

今年3月份 , Intel、台积电、三星、日月光、AMD、ARM、高通、Google、微软、Meta(Facebook)等行业巨头联合 , 打造了全新的通用芯片互联标准——UCle 。

芯动科技随后宣布 , 率先推出国产自主研发的物理层兼容UCIe国际标准的IP解决方案“Innolink Chiplet” , 是国内首套跨工艺、跨封装的Chiplet连接解决方案 , 并且在先进工艺上量产验证成功 。

据芯动科技Chiplet架构师高专介绍 , 芯动科技在Chiplet技术领域积累了大量的客户应用需求经验 , 并且和台积电、Intel、三星、美光等业界领军企业有密切的技术沟通和合作探索 , 两年前就开始了Innolink Chiplet的研发工作 , 率先明确Innolink B/C基于DDR的技术路线 , 并于2020年的Design Reuse全球会议上首次向业界公开Innolink A/B/C技术 。

得益于正确的技术方向和超前的布局规划 , Innolink的物理层与UCIe的标准保持一致 , 成为国内始发、世界先进的自主UCIe Chiplet解决方案 。

芯动科技在Innolink-B/C方案中采用了DDR的方式实现 , 提供基于GDDR6/LPDDR5技术的高速、高密度、高带宽连接方案 。

标准封装使用MCM传统基板或短距PCB , 作为Chiplet互联的介质 , 具备成本便宜、集成容易等特点 , 同时搭配先进封装比如Silicon Interposer , 具备密度高、功耗低、成本高等特点 。

目前 , Innolink Chiplet方案不仅用在风华1号数据中心GPU上 , 实现了性能翻倍 , 还被授权给了众多合作伙伴和客户 。

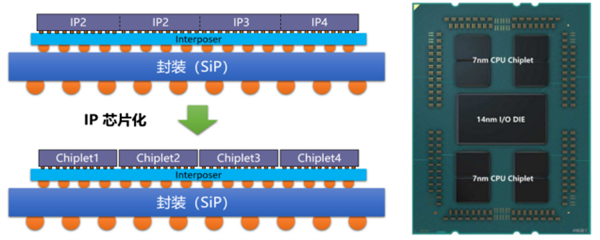

通过复用芯动科技的国产Innolink Chiplet技术 , 芯片设计企业和系统厂商能够快速便捷地实现多Die、多芯片之间的互连 , 有效简化了设计流程 。

目前 , 芯动科技科已经掌握了GDDR6/6X、LPDDR5/5X、DDR5/4、HBM3/HBM2E、32G/56G SerDes、基板和Interposer设计方案、高速信号完整性分析、先进工艺封装、测试方法等等世界前沿的核心技术 , 并且经过大量客户需求落地和量产验证迭代 , 累计流片200次以上的验证经验 , 高端IP出货超60亿颗的量产应用 。

尤其在DDR系列高带宽技术上 , 芯动科技以先进FinFet工艺量产了全球最快的LPDDR5/5X/DDR5 IP一站式解决方案 , 首次在普通PCB长距离上 , 实现内存颗粒过10Gbps的访问速率 。

相关经验推荐

- |操作系统领域,不再是美国厂商说了算,中国力量崛起了

- 苹果|比芯片断供更可怕?美国宣布新禁令,中国院士说得很对

- 存储卡|受全球芯片短缺影响最严重的四个行业,你知道几个?

- 交换机|起售价不足5000!华为mate50搭载骁龙芯片,支持100W充电?

- 华为|三星正式官宣“回归”中国市场,多项计划直指华为?

- 腾讯|缺点明显、价格偏贵!iPhone13上市一年,为何依旧吸引中国消费者?

- 芯片|格芯拿下高通500亿芯片大单!中芯国际等中资厂商缘何失之交臂?

- 芯片|亡羊补牢?芯片的决定已经出炉,张忠谋说得非常对

- |我国有没有显卡公司?为什么大家只看到美国显卡?

- 芯片|3年周旋终落地,美芯片“卡脖”手段再升级,中国芯片如何应对?

![时光公主礼物制作图大全:礼物合成配方攻略[多图]](http://img1.jingyanla.com/220423/0451563236-0-lp.jpg)