文章插图

文章插图

文章插图

本报(chinatimes.net.cn)采访人员陶炜 张智 南京报道

国产封测厂商正在Chiplet(小芯粒)技术方向上加速奔跑 。

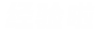

1月5日,长电科技(600584.SH)在其公众号上宣布,公司XDFOI?Chiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,同步实现国际客户4nm节点多芯片系统集成封装产品出货,最大封装体面积约为1500mm2的系统级封装 。而早在一年之前,另一家国产封测巨头通富微电就已经在2021年年报中宣布 , 公司已大规模生产Chiplet产品,7nm产品已大规模量产,5nm产品已完成研发即将量产 。

在摩尔定律已接近极致的当下,Chiplet技术由于可以有效的平衡芯片效能、成本以及良率之间的关系,近年来深受人们关注 。尤其是在国产芯片遭遇种种技术封锁的背景下,人们对于国产芯片通过Chiplet技术绕开先进制程领域遭到的封锁饱含期待 。

【国产封测厂商竞速Chiplet,能否突破芯片技术封锁?】不过 , 采访人员在采访中了解到 , 先进封装并不能完全取代先进制程的作用 , 但确实能够在一定程度上突破封锁 。“相比SoC , 小芯粒具有以下特点:可以重复使用的IP,异构集成,高良率 。这些特点可以降低传统封装的成本,在某种条件下可以降低对先进制程的依赖程度,但依然对先进工艺有较高要求 。”深度科技研究院院长张孝荣对《华夏时报》采访人员表示 。

国产封测企业竞速Chiplet

1月5日 , 长电科技宣布,公司XDFOI? Chiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,同步实现国际客户4nm节点多芯片系统集成封装产品出货 , 最大封装体面积约为1500mm2的系统级封装 。

所谓Chiplet , 通常被翻译为“粒芯”或“小芯片” , 单从字面意义上可以理解为“粒度更小的芯片” 。它是一种在先进制程下提升芯片的集成度 , 在不改变制程的前提下提升算力,并保证芯片制造良品率的一种手段 。在当下,Chiplet技术被认为是在摩尔定律接近极致的情况下继续提高芯片性能的希望所在 。

传统的系统级单芯片(SoC)将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆上 。随着先进工艺节点不断演进,单颗芯片上可容纳的晶体管数量及单位面积性能不断提升 。以 80mm面积的芯片裸片为例,在16nm工艺节点下,单颗裸片可容纳的晶体管数量为21.12 亿个;在7nm工艺节点下,该晶体管数量可增长到69.68亿个 。然而随着半导体工艺的进步,在同等面积大小的区域里,挤进越来越多的硅电路,漏电流增加、散热问题大、时钟频率增长减慢等问题难以解决,芯片设计的难度和复杂度也在进一步增加 。随着半导体工艺节点越来越接近物理极限 , 每一代半导体工艺节点提升对于芯片性能带来的收益也越来越小 。

而Chiplet技术,在封装系统里面不再使用少量的大芯片做集成,而是改用数量更多但是尺寸更小的芯片粒(Chiplet)作为基本单位 。其实现原理如同搭积木一样,把一些预先在工艺线上生产好的实现特定功能的芯片裸片,再将这些模块化的小芯片(裸片)互连起来,通 过先进的集成技术(如3D集成等)集成封装在一起,从而形成一个异构集成系统芯片 。

“Chiplet 封装带来的是对传统片上系统集成模式的革新 , 主要表现在:1,良率提升:降低单片晶圆集成工艺良率风险 , 达到成本可控,有设计弹性 , 可实现芯片定制化;2,Chiplet将大尺寸的多核心的设计 , 分散到较小的小芯片,更能满足现今高效能运算处理器的需求;3,弹性的设计方式不仅提升灵活性,且可实现包括模块组装、芯片网络、异构系统与元件集成四个方面的功能,从而进一步降低成本(例如某些对于逻辑性能需求不高的模组可以使用成熟工艺)并提升性能 。”长江证券分析师杨洋指出,基于小芯片的面积优势,Chiplet 可以大幅提高大型芯片的良率 。目前在高性能计算、AI等方面的巨大运算需求,推动了逻辑芯片内的运算核心数量快速上升,与此同时,配套的SRAM容量、I/O数量也在大幅提升,使得整个芯片不仅晶体管数量暴涨,芯片的面积也不断增大 。通过Chiplet设计将大芯片分成更小的芯片可以有效改善良率,同时也能够降低因为不良率而导致的成本增加,多芯片集成在越先进工艺下(如5nm)越具有显著的优势 , 因为在800mm面积的单片系统中,硅片缺陷导致的额外成本占总制造成本的50%以上 。

相关经验推荐

- 乘联会崔东树:近日国产特斯拉降价是正常趋势,碳酸锂价格将大跌

- 辉瑞新冠药为何未进医保目录,对国产在研新冠口服药影响几何

- 特斯拉3个月降价近20%,国产品牌怎么办?

- 以军官开中国产汽车,美国据此劝告以色列:双重国籍者不得驾驶F-35

- 辉瑞缘何谈崩? 高定价医保“无法妥协” 国产类似产品价格大概率500元以下 | 行业动态

- 本月最火的国产剧,开播就拿下收视冠军,央视又拿出一部王炸

- 2022最值得二刷的6部韩剧,每部都甩今年的国产剧好几条街

- 亲自感受抑郁 国产游戏《抑郁的房间》上架Steam商店

- EVO2022新增直播节目 万代等多家厂商将公布新内容

- 国产大飞机C919累计获得订单超千架