|【专利解密】芯导科技技术沉淀 发明双向TVS器件制备方案

文章图片

【嘉勤点评】芯导科技发明的双向TVS器件及其制备方法 , 相对于嵌入普通二极管的结构形式 , 该方案中的结构不仅可有效避免有源区面积减小后ESD防护能力弱的问题 , 也具备制造工艺简单的优点 , 从而可以降低其制造成本 。

集微网消息 , 11月12日 , 芯导科技发布科创板上市招股意向书、上市发行安排及初步询价公告 , 预计近期将正式登陆科创板上市 。 其在TVS、MOSFET、肖特基等功率器件方面具有较强的技术积累 , 同时拥有良好的市场口碑 。

TVS器件 , 可理解为瞬态二极管 , 这是一种二极管形式的高效能保护器件 。 TVS器件能在极短时间内承受反向电压冲击 , 使两极间的电压钳位于一个特定电压上 , 避免后面的电路受到冲击 。 其中 , 双向TVS器件可在正反两个方向吸收瞬时大脉冲 。

目前市场上有多种低电容双向TVS器件的产品结构中:对于电容值在1pF以下的TVS器件 , 通常在器件结构中串联普通二极管的方式降低整体电容;对于电容值在2~5pF范围的TVS器件 , 通常采用减小有源区的面积来满足容值的需求 。

但是减小有源区面积的同时 , TVS器件的浪涌能力以及ESD防护能力也会随之减小 , 这与市场需求的低电容产品高ESD防护能力相矛盾 , 因此 , 仅仅减小有源区面积很难满足器件高浪涌、高ESD防护能力的需求 。

为解决该难题 , 芯导科技在2021年8月20日申请了一项名为“双向TVS器件及其制备方法、电子设备”的发明专利(申请号:202110958513.3) , 申请人为上海芯导电子科技股份有限公司 。

根据该专利目前公开的相关资料 , 让我们一起来看看这项技术方案吧 。

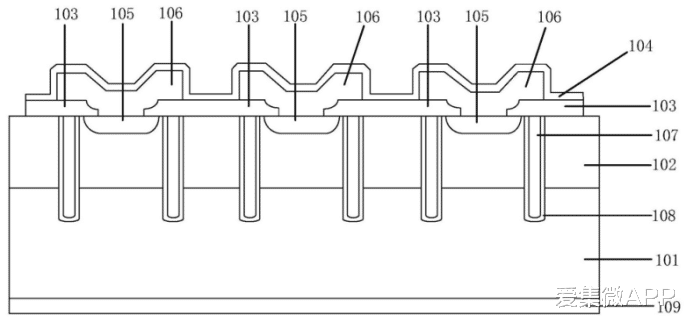

如上图 , 为该专利中发明的双向TVS器件的结构示意图 , 这种双向TVS器件包括:衬底101、外延层102、有源区105、隔离槽、主氧化层103、图形化的第一金属层106以及第二金属层109 。 其中 , 外延层设置于衬底的上侧方 , 其材料通常选用P型外延层 , 且厚度可根据需求进行配置 。

隔离槽从外延层的表面延申至沉底内 , 其贯穿外延层而延申至衬底内 , 其具有的隔离功能可以将使得各有源区分隔独立 , 能够防止各个有源区之间横向电场的干扰 。 基于隔离槽的深度 , 可以将不同的外延层部隔离开来 , 并且其中填充有槽内多晶硅107 。 在这种结构中 , 有源区为N+有源区 , 衬底为N型衬底 , 外延层为P型外延层 , 因此三者可形成NPN结构 。

该方案基于填充有多晶硅的隔离槽 , 其贯穿外延层而延伸至衬底 , 因此可改善PN结结边缘的电势分布 , 增强器件的防浪涌能力 , 同时 , 槽内填充的多晶硅也可进一步提升防浪涌能力 。

此外 , 该双向TVS器件还包括有钝化层104 , 钝化层设置于主氧化层和第一金属层的相背于外延层的一侧 , 其能够减少氧化层中的各种电荷 , 可以保护电路及内部互连线免受机械和化学损伤 , 达到增强器件对离子玷污的阻挡能力 , 从而起到保护作用的材料层 。

如上图 , 为这种双向TVS器件的制备方法的流程示意图 , 该方案首先在衬底上生长外延层 。 当有了外延层后 , 即可在其上制作隔离槽 , 并在隔离槽内填充槽内多晶硅 , 其中需要执行包括掩膜形成、刻蚀、生长等多个步骤 。

其次 , 在对应的两个隔离槽间的外延层部分形成有源区域 , 第一PN结和第二PN结就形成于该区域中 。 并且外延层、有源区域和隔离槽的槽口沉淀主氧化层 , 在主氧化层上刻蚀出接触孔 , 通过接触孔图形化第一金属材料 , 其穿过接触孔与有源区连接 。

相关经验推荐

- 酷睿处理器|11/12代酷睿+Win11封杀4K蓝光碟 播放软件厂商回应:无能为力

- |司马南炮轰联想的背后,导致联想产生危机的原因是什么?

- 科技创新|吐槽一下三星s21网络问题

- 华为手机|华为手机拍照不好看?新手必看指南

- 苹果|重夺智能手机头把交椅,iPhone为苹果贡献2000亿美元收入

- 华为|华为满足了我们的的民族自豪感,高端手机,不止外国人可以玩的溜

- 清华大学|挚听32通道智能助听器,清华专利技术,支持智能验配

- 努比亚|小米和OV的定位就不同,配置控适合小米,追星族适合OV

- |过年还在宅家玩手机?不如来刷这个电工题库!考试惊艳所有人

- 一加科技|可旋转180度巨大背面单摄渲染图曝光 一加全新影像专利一颗顶三个